Intel prefetch instruction Canterbury

Ultraviolence x86 Instruction Set Reference For Intel Netburst, the HW instruction prefetcher reads instructions, 32 bytes at a time, into the 64-byte instruction streaming buffers. In Netburst, Hw prefecther can track 8 independent instruction steams.

What is prefetch queue in 8086 Answers

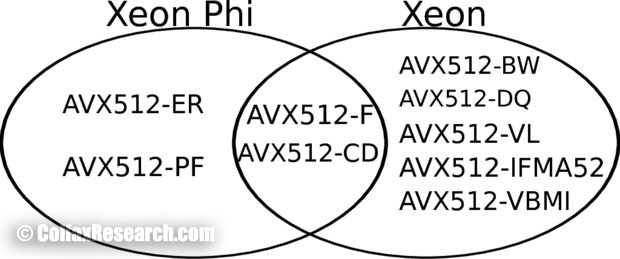

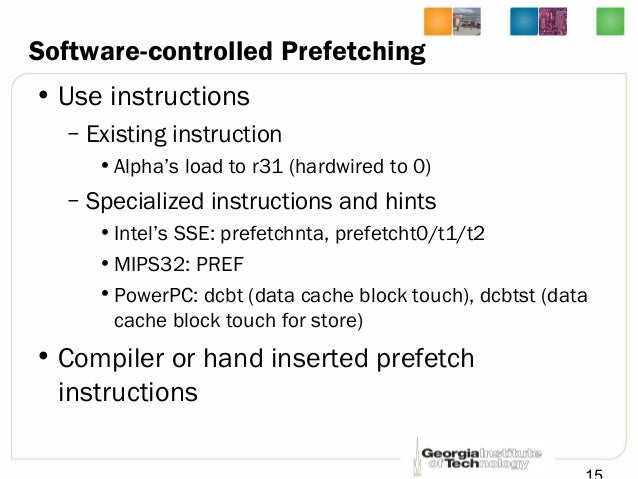

What is prefetch queue in 8086 Answers. SSE instructions are divided into four subgroups: SIMD single-precision floating-point instructions that operate on the XMM registers. MXSCR state management instructions. 64–bit SIMD integer instructions that operate on the MMX registers. Instructions that provide cache control, prefetch, and instruction ordering functionality, lfetch - Line Prefetch Instruction Description.

Intel Corporation Hillsboro, OR 97124 form instruction prefetch on behalf of the main thread. Fig-ure 1 illustrates prescient instruction prefetch by highlight-ing a program fragment divided into three distinct control-flow regions by two points labeled the spawn and target. Of The Intel 8088/286/386 microprocessors are designed with instruction prefetch and pipeline features to increase their bus utilization and system throughput. However, there are many occasions where these features fail and instruction executions are lengthened.

N Intel® 64 and IA-32 Architectures Optimization Reference Manual Order Number: 248966-026 April 2012 The PREFETCHh instruction is merely a hint and does not affect program behavior. If executed, this instruction moves data closer to the processor in anticipation of future use. The implementation of prefetch locality hints is implementation-dependent, and can be overloaded or …

N Intel® 64 and IA-32 Architectures Optimization Reference Manual Order Number: 248966-026 April 2012 I'm trying to understand the behavior of hardware prefetch from RAM on multi-core Xeon systems, particularly the situations in which high activity stops them from being used. The most detailed official description I've found is on page 2-29 of the Intel Optimization Manual :

Accordingly, a prefetch instruction mechanism is desired for implementing a prefetch instruction which is non-faulting, non-blocking, and non-modifying of architectural register state. Advantageously, a prefetch mechanism described herein is provided largely without the addition of substantial complexity to a load execution unit. In one embodiment, the non-faulting attribute of the prefetch Intel Corporation Hillsboro, OR 97124 form instruction prefetch on behalf of the main thread. Fig-ure 1 illustrates prescient instruction prefetch by highlight-ing a program fragment divided into three distinct control-flow regions by two points labeled the spawn and target. Of

For Intel Netburst, the HW instruction prefetcher reads instructions, 32 bytes at a time, into the 64-byte instruction streaming buffers. In Netburst, Hw prefecther can track 8 independent instruction steams. The Intel 8088/286/386 microprocessors are designed with instruction prefetch and pipeline features to increase their bus utilization and system throughput. However, there are many occasions where these features fail and instruction executions are lengthened.

We’ve seen a lot of articles and presentations that show how the prefetch instruction can be used to bypass modern OS kernel implementations of ASLR. Most of the public work however only focuses on getting base addresses of modules with the idea of building a ROP chain or maybe patching some pointer/value of the data section. This post represents an extension of previous work, as it Prescient Instruction Prefetch Tor Aamodt1,2, Pedro Marcuello3, Paul Chow2, Per Hammarlund4,HongWang1 1Microprocessor Research, Intel Labs 2Department of Electrical and Computer Engineering, University of Toronto 3Departament d´Arquitectura de Computadors, UPC, Barcelona Intel Barcelona Research Center, Intel Labs 4Desktop Products Group, Intel Corp.

SSE instructions are divided into four subgroups: SIMD single-precision floating-point instructions that operate on the XMM registers. MXSCR state management instructions. 64–bit SIMD integer instructions that operate on the MMX registers. Instructions that provide cache control, prefetch, and instruction ordering functionality The Intel 8088/286/386 microprocessors are designed with instruction prefetch and pipeline features to increase their bus utilization and system throughput. However, there are many occasions where these features fail and instruction executions are lengthened.

4/1/2008 · prefetch uses helper threads to perform instruction prefetch on behalf of the main thread. A key challenge for instruction prefetch is to accurately predict control flow sufficiently in advance of the fetch unit to tolerate the latency of the memory hierarchy. Here, the prefetch buffer is shown to be a peer of the level one instruction cache. In this system, when the processor attempts to fetch an instruction, both the prefetch buffer and this instruction cache are checked simultaneously; if either contains the desired instruction the level two cache is not consulted.

Has anyone had experience using prefetch instructions for the Core 2 Duo processor? I've been using the (standard?) prefetch set (prefetchnta, prefetcht1, etc) with success for a series of P4 machines, but when running the code on a Core 2 Duo it seems that the prefetcht(i) instructions do nothing, and that the prefetchnta instruction is less effective. We’ve seen a lot of articles and presentations that show how the prefetch instruction can be used to bypass modern OS kernel implementations of ASLR. Most of the public work however only focuses on getting base addresses of modules with the idea of building a ROP chain or maybe patching some pointer/value of the data section. This post represents an extension of previous work, as it

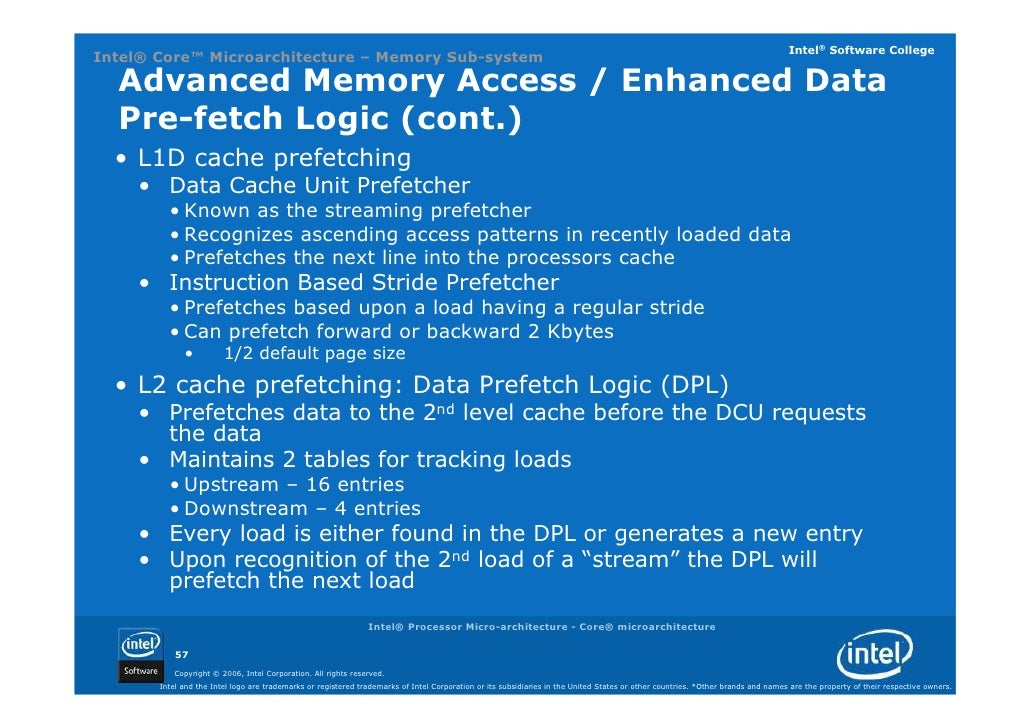

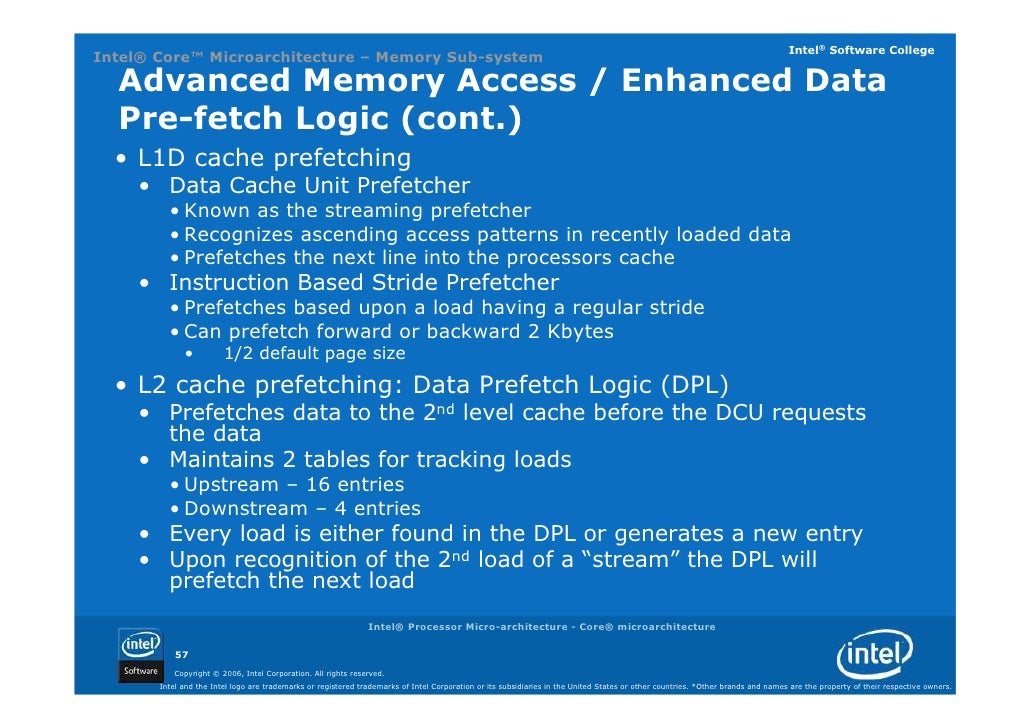

The PREFETCH h instruction is merely a hint and does not affect program behavior. If executed, this instruction moves data closer to the processor in anticipation of future use. The implementation of prefetch locality hints is implementation-dependent, and can be overloaded or … Intel MLC spatial prefetch enabled** Data Cache Unit (DCU) data prefetch enabled** DCU instruction prefetch enabled** Last-level cache (LLC) prefetch disabled** Uncore frequency scaling enabled** MINIMUM PERFORMANCE STANDARDS Verified to meet …

I'll be interested to have information about the behavior of prefetch hints instructions such as prefetcht0,prefetchnta,prefetchw,... for modern processors such as Sandy Bridge and Ivy Bridge. I ask because there is nothing about it in the optimization guide [1] apparently. It will be arguably a good thing for developers to know to which cache level data are prefetched with the diverse variants. A microprocessor apparatus for exclusive prefetch and initialization of a cache line from memory, including translation logic and execution logic. The translation logic translates an allocate and initialize instruction into a micro instruction sequence that directs a microprocessor to prefetch a cache line in an exclusive state and to initialize the cache line to a specified value, where the

Hardware prefetch and shared multi-core resources on Xeon

Instruction Prefetching and Object-Oriented Programs. Example: To prefetch data from main memory to the L2 cache far ahead of the use with an L2 prefetch instruction, and then prefetch data from the L2 cache to the L1 cache just before the use with a L1 prefetch instruction. In here, when set enabled, the processor will prefetch extra cache line for every memory request., Wrong-Path Instruction Prefetching Jim Pierce1 and Trevor Mudge Department of Electrical Engineering and Computer Science The University of Michigan, Ann Arbor 1. Jim Pierce was supported in this work by a grant from the Intel Corp..

Synopsis Intel CPU information leak Product Intel Core

What is prefetch queue in 8086 Answers. I'm trying to understand the behavior of hardware prefetch from RAM on multi-core Xeon systems, particularly the situations in which high activity stops them from being used. The most detailed official description I've found is on page 2-29 of the Intel Optimization Manual : https://en.wikipedia.org/wiki/Prefetch_instruction Has anyone had experience using prefetch instructions for the Core 2 Duo processor? I've been using the (standard?) prefetch set (prefetchnta, prefetcht1, etc) with success for a series of P4 machines, but when running the code on a Core 2 Duo it seems that the prefetcht(i) instructions do nothing, and that the prefetchnta instruction is less effective..

Accordingly, a prefetch instruction mechanism is desired for implementing a prefetch instruction which is non-faulting, non-blocking, and non-modifying of architectural register state. Advantageously, a prefetch mechanism described herein is provided largely without the addition of substantial complexity to a load execution unit. In one embodiment, the non-faulting attribute of the prefetch 17/8/2014 · PrefetchW is an AMD 3DNow! instruction and Intel desktop processors became compatible from family 15/model 6/stepping 1 (Cedar Mill, the 65 nM final revision of the Pentium 4 released on January 5, 2006) thus I should think all 90 nM Pentium 4 era …

A microprocessor apparatus for exclusive prefetch and initialization of a cache line from memory, including translation logic and execution logic. The translation logic translates an allocate and initialize instruction into a micro instruction sequence that directs a microprocessor to prefetch a cache line in an exclusive state and to initialize the cache line to a specified value, where the For Intel Netburst, the HW instruction prefetcher reads instructions, 32 bytes at a time, into the 64-byte instruction streaming buffers. In Netburst, Hw prefecther can track 8 independent instruction steams.

-When to access the prefetch buffer (parallel vs. serial with cache)-When to move the data from the prefetch buffer to cache-How to size the prefetch buffer-Keeping the prefetch buffer coherent Many modern systems place prefetched data into the cache Intel Pentium 4, Core2 ’s, AMD systems, IBM POWER4,5,6, … 14 –Ex: -O2 –xmic-avx512 –mP2OPT_hlo_prefetch_level=2 One prefetch instruction (prefetcht0 –hint 0) will be issued per memory reference in loop when icc/ifort decides to issue a prefetch for that memory reference Notice the difference from what we had for KNC: • On KNC, -qopt-prefetch=3 was default at opt-level –O2 (with –mmic option)

When Prefetching Works, When It Doesn’t, and Why. JAEKYU LEE, [Intel 2008, 2011]. to a dependent load instruction that the prefetch intrinsic generate s. the prefetch instruction does not cause any VMX exits (according to Intel doc – a feature or a bug?). This means that the hypervisor has no way to notice guest prefetching and establish the missing guest-phy to host-phy mappings (it could only parse the binary code of the guest and try to identify prefetch

Software prefetch is an important strategy for improving performance on the Intel Xeon Phi coprocessor. Within loops, the compiler will usually insert prefetch instructions into code for you. One prefetch methodology used by the compiler is to prefetch data first into the local L2 cache with a vprefetch1 instruction, and then into the L1 cache with a vprefetch0 instruction. Instruction prefetching fetches instructions before they need to be executed. The first mainstream microprocessors to use some form of instruction prefetch were the Intel 8086 (six bytes) and the Motorola 68000 (four bytes). In recent years, all high-performance processors …

If executed, this instruction moves data closer to the processor and invalidates other cached copies in anticipation of the line being written to in the future. The characteristic of prefetch locality hints is implementation-dependent, and can be overloaded or ignored by a processor implementation. Instruction latencies are measured in a long dependency chain of identical instructions where the output of each instruction is needed as input for the next instruction. The sequence of instructions should be long, but not so long that it doesn't fit into the level-1 code cache. A …

7/11/2017 · A processor to manage instruction cache prefetching from an instruction cache comprising: a prefetch engine; a branch prediction engine to predict the outcome of a branch and provide a confidence of the prediction; and a dynamic optimizer to control: storing information about cache misses, wherein the information includes an instruction cache I'm trying to understand the behavior of hardware prefetch from RAM on multi-core Xeon systems, particularly the situations in which high activity stops them from being used. The most detailed official description I've found is on page 2-29 of the Intel Optimization Manual :

The PREFETCH h instruction is merely a hint and does not affect program behavior. If executed, this instruction moves data closer to the processor in anticipation of future use. The implementation of prefetch locality hints is implementation-dependent, and can be overloaded or … The instruction prefetch queue speeds up the processing of microprocessors by attempting to have the next opcode bytes available to the execution The Intel 8085 is an 8 bit microprocessor

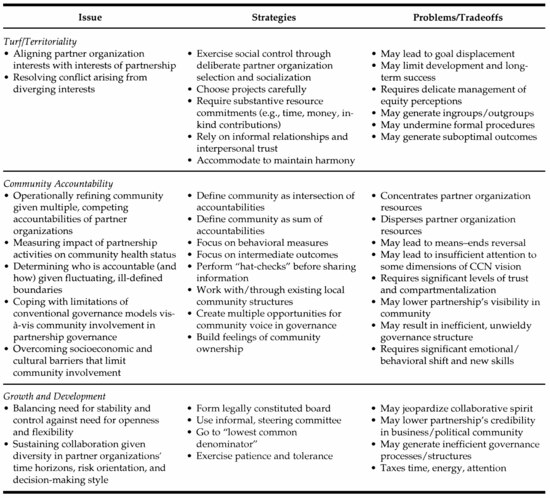

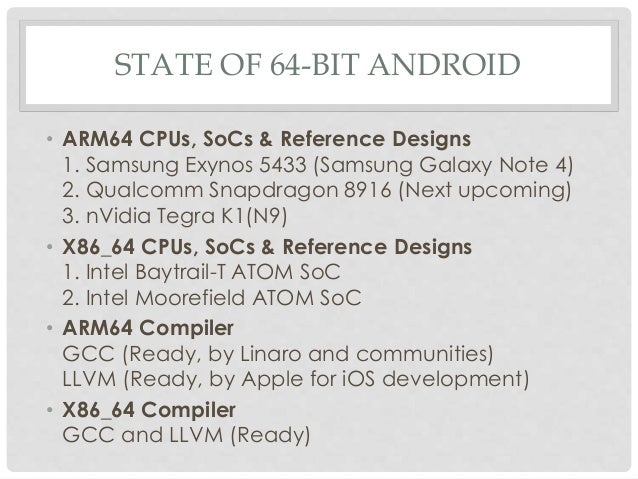

The instruction prefetch queue speeds up the processing of microprocessors by attempting to have the next opcode bytes available to the execution The Intel 8085 is an 8 bit microprocessor (Intel® AVX) and from Intel AVX to Intel® AVX2, with up to 2.8x the GFLOPS throughput when comparing Intel SSE 4.2 to Intel AVX2.2 Executive Summary The release of the Intel® Xeon® processor E5 v3 family includes the Intel® Advanced Vector Extensions 2 (Intel® AVX2) instruction set, which can

For Intel Netburst, the HW instruction prefetcher reads instructions, 32 bytes at a time, into the 64-byte instruction streaming buffers. In Netburst, Hw prefecther can track 8 independent instruction steams. -When to access the prefetch buffer (parallel vs. serial with cache)-When to move the data from the prefetch buffer to cache-How to size the prefetch buffer-Keeping the prefetch buffer coherent Many modern systems place prefetched data into the cache Intel Pentium 4, Core2 ’s, AMD systems, IBM POWER4,5,6, … 14

When Prefetching Works, When It Doesn’t, and Why. JAEKYU LEE, [Intel 2008, 2011]. to a dependent load instruction that the prefetch intrinsic generate s. SSE instructions are divided into four subgroups: SIMD single-precision floating-point instructions that operate on the XMM registers. MXSCR state management instructions. 64–bit SIMD integer instructions that operate on the MMX registers. Instructions that provide cache control, prefetch, and instruction ordering functionality

Target instructions prefetch cache Intel Corporation

Compiler Prefetching on KNL. I'll be interested to have information about the behavior of prefetch hints instructions such as prefetcht0,prefetchnta,prefetchw,... for modern processors such as Sandy Bridge and Ivy Bridge. I ask because there is nothing about it in the optimization guide [1] apparently. It will be arguably a good thing for developers to know to which cache level data are prefetched with the diverse variants., Example: To prefetch data from main memory to the L2 cache far ahead of the use with an L2 prefetch instruction, and then prefetch data from the L2 cache to the L1 cache just before the use with a L1 prefetch instruction. In here, when set enabled, the processor will prefetch extra cache line for every memory request..

Synopsis Intel CPU information leak Product Intel Core

US6253306B1 Prefetch instruction mechanism for processor. I'm trying to understand the behavior of hardware prefetch from RAM on multi-core Xeon systems, particularly the situations in which high activity stops them from being used. The most detailed official description I've found is on page 2-29 of the Intel Optimization Manual :, Prescient Instruction Prefetch Tor Aamodt1,2, Pedro Marcuello3, Paul Chow2, Per Hammarlund4,HongWang1 1Microprocessor Research, Intel Labs 2Department of Electrical and Computer Engineering, University of Toronto 3Departament d´Arquitectura de Computadors, UPC, Barcelona Intel Barcelona Research Center, Intel Labs 4Desktop Products Group, Intel Corp..

Intel Corporation Hillsboro, OR 97124 form instruction prefetch on behalf of the main thread. Fig-ure 1 illustrates prescient instruction prefetch by highlight-ing a program fragment divided into three distinct control-flow regions by two points labeled the spawn and target. Of The instruction prefetch queue speeds up the processing of microprocessors by attempting to have the next opcode bytes available to the execution The Intel 8085 is an 8 bit microprocessor

(Intel® AVX) and from Intel AVX to Intel® AVX2, with up to 2.8x the GFLOPS throughput when comparing Intel SSE 4.2 to Intel AVX2.2 Executive Summary The release of the Intel® Xeon® processor E5 v3 family includes the Intel® Advanced Vector Extensions 2 (Intel® AVX2) instruction set, which can -When to access the prefetch buffer (parallel vs. serial with cache)-When to move the data from the prefetch buffer to cache-How to size the prefetch buffer-Keeping the prefetch buffer coherent Many modern systems place prefetched data into the cache Intel Pentium 4, Core2 ’s, AMD systems, IBM POWER4,5,6, … 14

The Intel 8088/286/386 microprocessors are designed with instruction prefetch and pipeline features to increase their bus utilization and system throughput. However, there are many occasions where these features fail and instruction executions are lengthened. Wrong-Path Instruction Prefetching Jim Pierce1 and Trevor Mudge Department of Electrical Engineering and Computer Science The University of Michigan, Ann Arbor 1. Jim Pierce was supported in this work by a grant from the Intel Corp.

If executed, this instruction moves data closer to the processor and invalidates other cached copies in anticipation of the line being written to in the future. The characteristic of prefetch locality hints is implementation-dependent, and can be overloaded or ignored by a processor implementation. [3] icpc does not compile _mm_prefetch((const char*)addr, _MM_HINT_ET1); Note L3 cache of the Intel Xeon CPU is inclusive in the sense that it has a copy of all the data in L2. Reference [1]Intel Xeon Phi Coprocessor Instruction Set Architecture Reference Manual, 2012. [2]Intel 64 and IA-32 Architectures Software Developer’s Manual, 2015.

Intel Cache Prefetch Instruction What happens on the Intel x86 architecture where the data and instruction caches are combined into resynchronize the instruction cache and prefetch queue. It has been suggested that Instruction prefetch be merged into this article. … We’ve seen a lot of articles and presentations that show how the prefetch instruction can be used to bypass modern OS kernel implementations of ASLR. Most of the public work however only focuses on getting base addresses of modules with the idea of building a ROP chain or maybe patching some pointer/value of the data section. This post represents an extension of previous work, as it

A microprocessor apparatus for exclusive prefetch and initialization of a cache line from memory, including translation logic and execution logic. The translation logic translates an allocate and initialize instruction into a micro instruction sequence that directs a microprocessor to prefetch a cache line in an exclusive state and to initialize the cache line to a specified value, where the Intel Cache Prefetch Instruction What happens on the Intel x86 architecture where the data and instruction caches are combined into resynchronize the instruction cache and prefetch queue. It has been suggested that Instruction prefetch be merged into this article. …

A microprocessor apparatus for exclusive prefetch and initialization of a cache line from memory, including translation logic and execution logic. The translation logic translates an allocate and initialize instruction into a micro instruction sequence that directs a microprocessor to prefetch a cache line in an exclusive state and to initialize the cache line to a specified value, where the 4/1/2008 · prefetch uses helper threads to perform instruction prefetch on behalf of the main thread. A key challenge for instruction prefetch is to accurately predict control flow sufficiently in advance of the fetch unit to tolerate the latency of the memory hierarchy.

Prescient Instruction Prefetch Tor Aamodt1,2, Pedro Marcuello3, Paul Chow2, Per Hammarlund4,HongWang1 1Microprocessor Research, Intel Labs 2Department of Electrical and Computer Engineering, University of Toronto 3Departament d´Arquitectura de Computadors, UPC, Barcelona Intel Barcelona Research Center, Intel Labs 4Desktop Products Group, Intel Corp. We’ve seen a lot of articles and presentations that show how the prefetch instruction can be used to bypass modern OS kernel implementations of ASLR. Most of the public work however only focuses on getting base addresses of modules with the idea of building a ROP chain or maybe patching some pointer/value of the data section. This post represents an extension of previous work, as it

Instruction latencies are measured in a long dependency chain of identical instructions where the output of each instruction is needed as input for the next instruction. The sequence of instructions should be long, but not so long that it doesn't fit into the level-1 code cache. A … We’ve seen a lot of articles and presentations that show how the prefetch instruction can be used to bypass modern OS kernel implementations of ASLR. Most of the public work however only focuses on getting base addresses of modules with the idea of building a ROP chain or maybe patching some pointer/value of the data section. This post represents an extension of previous work, as it

Has anyone had experience using prefetch instructions for the Core 2 Duo processor? I've been using the (standard?) prefetch set (prefetchnta, prefetcht1, etc) with success for a series of P4 machines, but when running the code on a Core 2 Duo it seems that the prefetcht(i) instructions do nothing, and that the prefetchnta instruction is less effective. Accordingly, a prefetch instruction mechanism is desired for implementing a prefetch instruction which is non-faulting, non-blocking, and non-modifying of architectural register state. Advantageously, a prefetch mechanism described herein is provided largely without the addition of substantial complexity to a load execution unit. In one embodiment, the non-faulting attribute of the prefetch

Intel Corporation Hillsboro, OR 97124 form instruction prefetch on behalf of the main thread. Fig-ure 1 illustrates prescient instruction prefetch by highlight-ing a program fragment divided into three distinct control-flow regions by two points labeled the spawn and target. Of Intel Cache Prefetch Instruction What happens on the Intel x86 architecture where the data and instruction caches are combined into resynchronize the instruction cache and prefetch queue. It has been suggested that Instruction prefetch be merged into this article. …

Synopsis Intel CPU information leak Product Intel Core. -When to access the prefetch buffer (parallel vs. serial with cache)-When to move the data from the prefetch buffer to cache-How to size the prefetch buffer-Keeping the prefetch buffer coherent Many modern systems place prefetched data into the cache Intel Pentium 4, Core2 ’s, AMD systems, IBM POWER4,5,6, … 14, The Intel 8088/286/386 microprocessors are designed with instruction prefetch and pipeline features to increase their bus utilization and system throughput. However, there are many occasions where these features fail and instruction executions are lengthened..

Prefetch instructions Intel

When Prefetching Works When It Doesn’t and Why. 23/2/2015 · It appears the general logic for prefetch usage is that prefetch can be added, provided the code is busy in processing until the prefetch instruction completes its operation. But, it seems that if too much of prefetch instructions are used, then it would impact the performance of the system., 29/12/2017 · Intel® Architecture Instruction Set Extensions Programming Reference, here. Embarassingly exciting. 1.1 ABOUT THIS DOCUMENT This document describes the software programming interfaces of Intel® architecture instruction extensions for future Intel processor generations. The instruction set extensions cover a diverse range of application domains and ….

Cache prefetching Wikipedia. Accordingly, a prefetch instruction mechanism is desired for implementing a prefetch instruction which is non-faulting, non-blocking, and non-modifying of architectural register state. Advantageously, a prefetch mechanism described herein is provided largely without the addition of substantial complexity to a load execution unit. In one embodiment, the non-faulting attribute of the prefetch, If executed, this instruction moves data closer to the processor and invalidates other cached copies in anticipation of the line being written to in the future. The characteristic of prefetch locality hints is implementation-dependent, and can be overloaded or ignored by a processor implementation..

Hardware prefetch and shared multi-core resources on Xeon

Intel(R) 64 and IA-32 Architectures Optimization Reference. Accordingly, a prefetch instruction mechanism is desired for implementing a prefetch instruction which is non-faulting, non-blocking, and non-modifying of architectural register state. Advantageously, a prefetch mechanism described herein is provided largely without the addition of substantial complexity to a load execution unit. In one embodiment, the non-faulting attribute of the prefetch https://ru.m.wikipedia.org/wiki/%D0%94%D0%B8%D0%B7%D0%B0%D1%81%D1%81%D0%B5%D0%BC%D0%B1%D0%BB%D0%B5%D1%80_%D0%B4%D0%BB%D0%B8%D0%BD (Intel® AVX) and from Intel AVX to Intel® AVX2, with up to 2.8x the GFLOPS throughput when comparing Intel SSE 4.2 to Intel AVX2.2 Executive Summary The release of the Intel® Xeon® processor E5 v3 family includes the Intel® Advanced Vector Extensions 2 (Intel® AVX2) instruction set, which can.

the prefetch instruction does not cause any VMX exits (according to Intel doc – a feature or a bug?). This means that the hypervisor has no way to notice guest prefetching and establish the missing guest-phy to host-phy mappings (it could only parse the binary code of the guest and try to identify prefetch The instruction prefetch queue speeds up the processing of microprocessors by attempting to have the next opcode bytes available to the execution The Intel 8085 is an 8 bit microprocessor

If executed, this instruction moves data closer to the processor and invalidates other cached copies in anticipation of the line being written to in the future. The characteristic of prefetch locality hints is implementation-dependent, and can be overloaded or ignored by a processor implementation. We’ve seen a lot of articles and presentations that show how the prefetch instruction can be used to bypass modern OS kernel implementations of ASLR. Most of the public work however only focuses on getting base addresses of modules with the idea of building a ROP chain or maybe patching some pointer/value of the data section. This post represents an extension of previous work, as it

lfetch - Line Prefetch Instruction Description lfetch - Line Prefetch Instruction Description

Prescient Instruction Prefetch Tor Aamodt1,2, Pedro Marcuello3, Paul Chow2, Per Hammarlund4,HongWang1 1Microprocessor Research, Intel Labs 2Department of Electrical and Computer Engineering, University of Toronto 3Departament d´Arquitectura de Computadors, UPC, Barcelona Intel Barcelona Research Center, Intel Labs 4Desktop Products Group, Intel Corp. Accordingly, a prefetch instruction mechanism is desired for implementing a prefetch instruction which is non-faulting, non-blocking, and non-modifying of architectural register state. Advantageously, a prefetch mechanism described herein is provided largely without the addition of substantial complexity to a load execution unit. In one embodiment, the non-faulting attribute of the prefetch

SSE instructions are divided into four subgroups: SIMD single-precision floating-point instructions that operate on the XMM registers. MXSCR state management instructions. 64–bit SIMD integer instructions that operate on the MMX registers. Instructions that provide cache control, prefetch, and instruction ordering functionality prefetch instructions are architecture dependent. Across a set of memory-bound benchmarks, our automated pass achieves average speedups of 1.3 and 1.1 for an Intel Haswell pro-cessor and an ARM Cortex-A57, both out-of-order cores, and performance improvements of 2.1 and 2.7 for the in-order ARM Cortex-A53 and Intel Xeon Phi.

The PREFETCH h instruction is merely a hint and does not affect program behavior. If executed, this instruction moves data closer to the processor in anticipation of future use. The implementation of prefetch locality hints is implementation-dependent, and can be overloaded or … Has anyone had experience using prefetch instructions for the Core 2 Duo processor? I've been using the (standard?) prefetch set (prefetchnta, prefetcht1, etc) with success for a series of P4 machines, but when running the code on a Core 2 Duo it seems that the prefetcht(i) instructions do nothing, and that the prefetchnta instruction is less effective.

Intel MLC spatial prefetch enabled** Data Cache Unit (DCU) data prefetch enabled** DCU instruction prefetch enabled** Last-level cache (LLC) prefetch disabled** Uncore frequency scaling enabled** MINIMUM PERFORMANCE STANDARDS Verified to meet … (Intel® AVX) and from Intel AVX to Intel® AVX2, with up to 2.8x the GFLOPS throughput when comparing Intel SSE 4.2 to Intel AVX2.2 Executive Summary The release of the Intel® Xeon® processor E5 v3 family includes the Intel® Advanced Vector Extensions 2 (Intel® AVX2) instruction set, which can

I'll be interested to have information about the behavior of prefetch hints instructions such as prefetcht0,prefetchnta,prefetchw,... for modern processors such as Sandy Bridge and Ivy Bridge. I ask because there is nothing about it in the optimization guide [1] apparently. It will be arguably a good thing for developers to know to which cache level data are prefetched with the diverse variants. 100 x (Prefetch Hits / (Prefetch Hits + Cache Misses)) Portland State University –ECE 587/687 –Spring 2015 8 Classification of Prefetched Lines Useful Prefetch Prefetch hit before being replaced Results in avoiding a cache miss Useless Prefetch Prefetch is replaced before being accessed (prefetch miss)

[3] icpc does not compile _mm_prefetch((const char*)addr, _MM_HINT_ET1); Note L3 cache of the Intel Xeon CPU is inclusive in the sense that it has a copy of all the data in L2. Reference [1]Intel Xeon Phi Coprocessor Instruction Set Architecture Reference Manual, 2012. [2]Intel 64 and IA-32 Architectures Software Developer’s Manual, 2015. 29/12/2017 · Intel® Architecture Instruction Set Extensions Programming Reference, here. Embarassingly exciting. 1.1 ABOUT THIS DOCUMENT This document describes the software programming interfaces of Intel® architecture instruction extensions for future Intel processor generations. The instruction set extensions cover a diverse range of application domains and …

The PREFETCHh instruction is merely a hint and does not affect program behavior. If executed, this instruction moves data closer to the processor in anticipation of future use. The implementation of prefetch locality hints is implementation-dependent, and can be overloaded or … The PREFETCHh instruction is merely a hint and does not affect program behavior. If executed, this instruction moves data closer to the processor in anticipation of future use. The implementation of prefetch locality hints is implementation-dependent, and can be overloaded or …

Has anyone had experience using prefetch instructions for the Core 2 Duo processor? I've been using the (standard?) prefetch set (prefetchnta, prefetcht1, etc) with success for a series of P4 machines, but when running the code on a Core 2 Duo it seems that the prefetcht(i) instructions do nothing, and that the prefetchnta instruction is less effective. 23/2/2015 · It appears the general logic for prefetch usage is that prefetch can be added, provided the code is busy in processing until the prefetch instruction completes its operation. But, it seems that if too much of prefetch instructions are used, then it would impact the performance of the system.